AMD planea acelerar la caché L2 en los futuros Ryzen

13:25, 19.01.2026

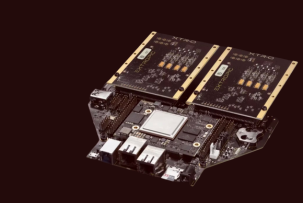

AMD planea una actualización radical de la arquitectura de sus futuros chips Ryzen mediante el uso de apilamiento vertical. Este enfoque permitirá aumentar el rendimiento y mejorar la eficiencia en los próximos procesadores Ryzen X3D.

Nueva tecnología — “Balanced Latency”

AMD ha presentado una patente para una tecnología llamada Balanced Latency Stacked Cache, cuyo objetivo es reducir la latencia en el acceso a los datos. El nuevo diseño de la caché L2 reduce la latencia de acceso de 14 a 12 ciclos por 1 MB.

Aunque esto pueda parecer una mejora menor, ahorrar incluso unos pocos ciclos puede tener un impacto significativo en la velocidad con la que los núcleos reciben instrucciones, así como en el rendimiento general y la eficiencia energética. Gracias a la estructura vertical y a la ubicación central de las interconexiones, los nuevos procesadores logran una aceleración notable.

¿Por qué es importante?

Aunque en la CES 2026 el título del procesador más rápido fue para el Ryzen 7 9850X3D, la implementación de caché L2 3D permitirá que los futuros procesadores gestionen mejor tareas como juegos con gráficos complejos. Incluso una reducción de solo dos ciclos puede traducirse en un aumento perceptible de los FPS.

Fecha de lanzamiento

Actualmente, la patente se encuentra en fase de desarrollo, lo que significa que AMD está experimentando con prototipos. Contar con una patente no garantiza que la tecnología llegue pronto al mercado, pero sí ofrece una visión clara del rumbo que está tomando la compañía.